# Selective Re-execution of Long-retired Misspeculated Instructions Using Forward Slicing

Smruti R. Sarangi, Wei Liu, Josep Torrellas, Yuanyuan Zhou

University of Illinois at Urbana-Champaign

http://iacoma.cs.uiuc.edu

- Predict the value and proceed speculatively

- When the correct value comes in, if misspediction, squash and re-execute

- Initial Proposals

- L1 data

- Data Dependences

- Aggressive Novel Proposals

- Values of L2 misses

- Thread independence in Thread-Level Speculation

- Speculative Synchronization

## **Long-latency Speculation**

- Misprediction recovery is very wasteful

- Most discarded instructions are still useful

ReSlice: Selective Re-Execution of Long-Retired Misspeculated Instructions Using Forward Slicing Wei Liu, University of Illinois 3

## **Contributions I**

ReSlice: Architecture to buffer forward slice and reexecute it on misprediction

## Contributions I

ReSlice: Architecture to buffer forward slice and reexecute it on misprediction

# Contributions II

- A Sufficient Condition

- Guarantee to correctly repair the program state

- Application to TLS:

- Speedup: geometric mean 12% over TLS

- E×D<sup>2</sup> reduction: 20%

#### Outline

7

- Motivation and Contributions

- Idea of ReSlice

- Architecture Design

- Experimental Results

- Conclusions

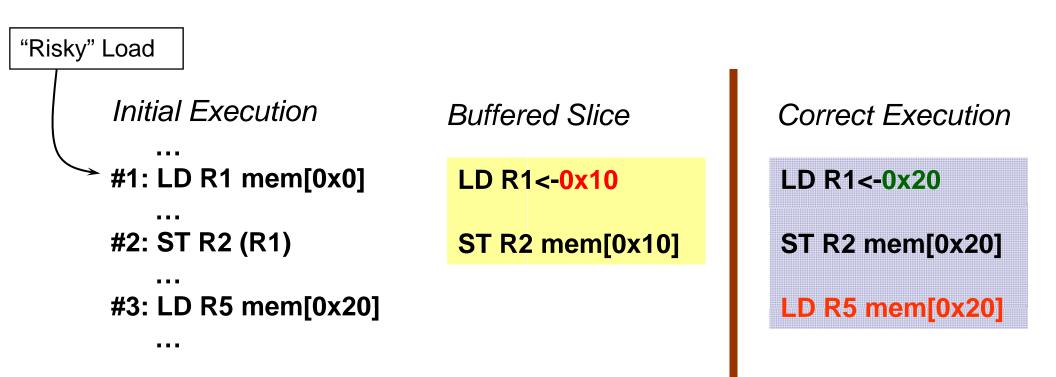

## Idea of ReSlice

- Initial execution of the task

- Predict value of "risky" load and continue

- Buffer in HW the forward slice of the load

- When a misprediction is confirmed

- Re-execute the slice with the new value

- If succeed: merge the register and memory state and continue

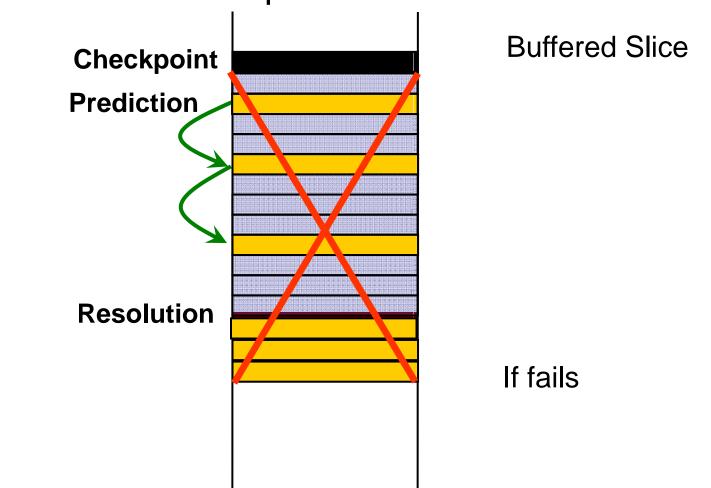

- If fail: revert to the conventional recovery: roll back and reexecute

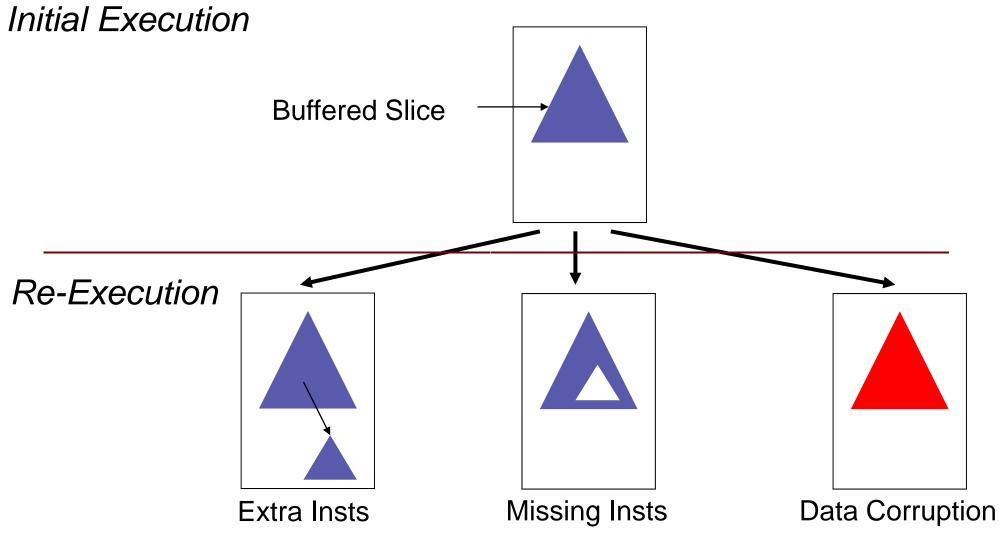

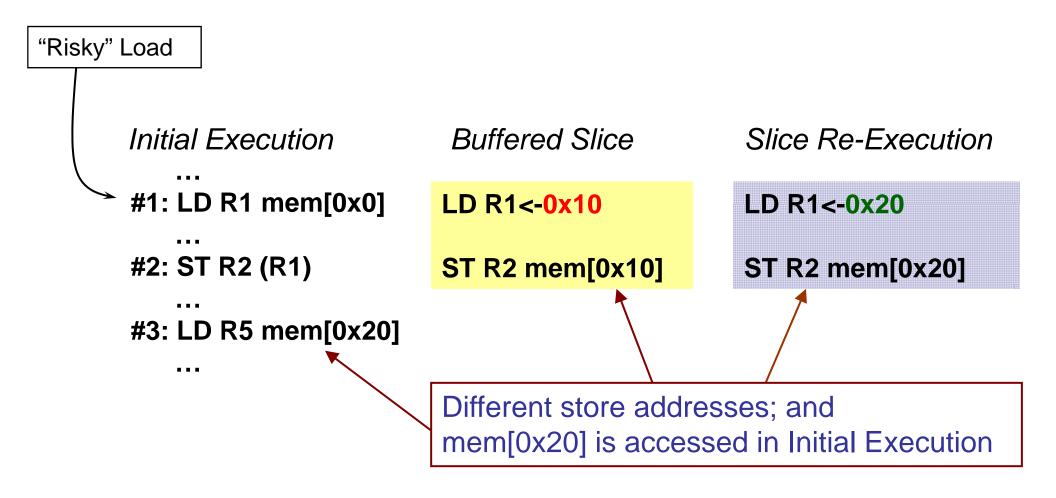

# Why is It Challenging?

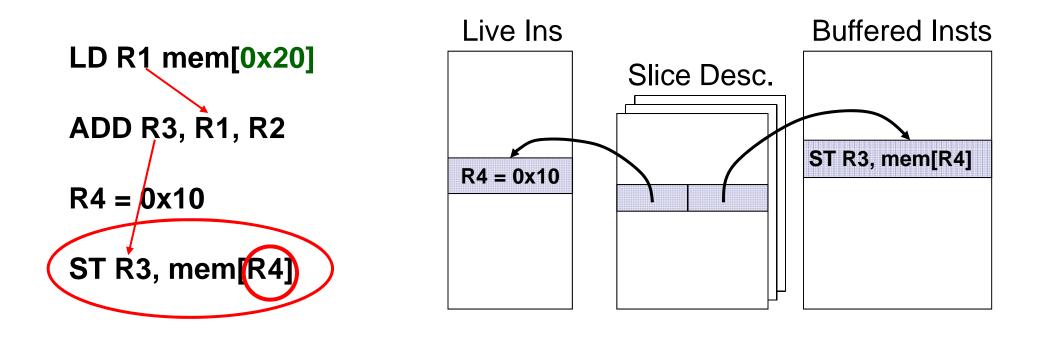

New values may induce new addresses => Slice changes

#### **Problem: Instruction #3 is not buffered!**

## **More Challenges**

## Solution: The Example Again

Run-time checking during slice re-execution

## A Sufficient Condition

- Guarantee Correct Slice Re-Execution and Merge

- Easy for HW to check at run-time

- Details please see our paper

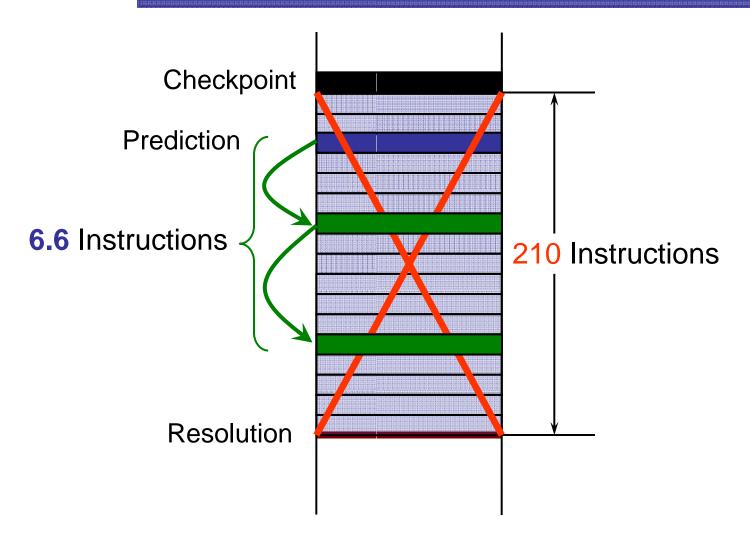

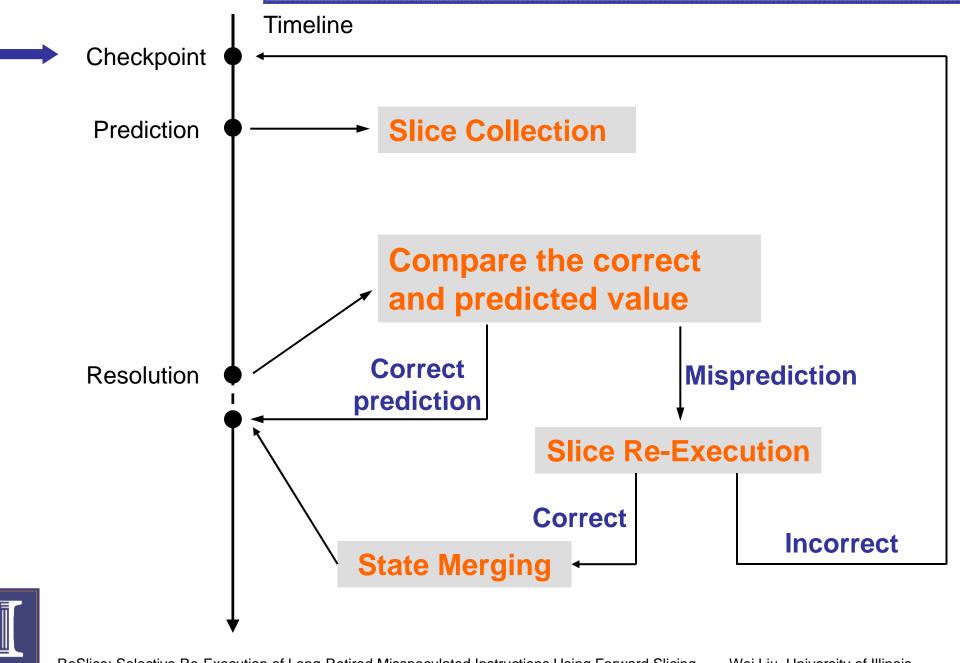

#### How does ReSlice work?

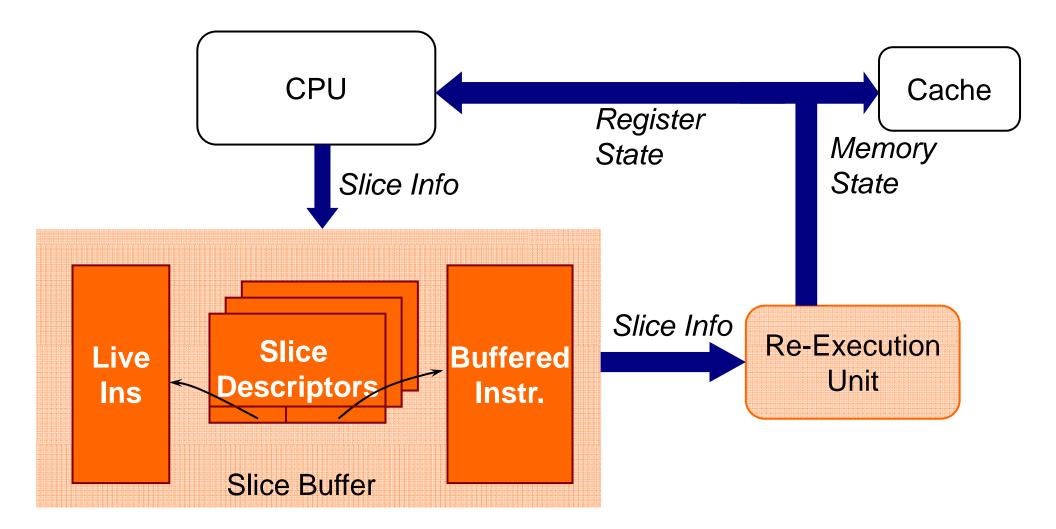

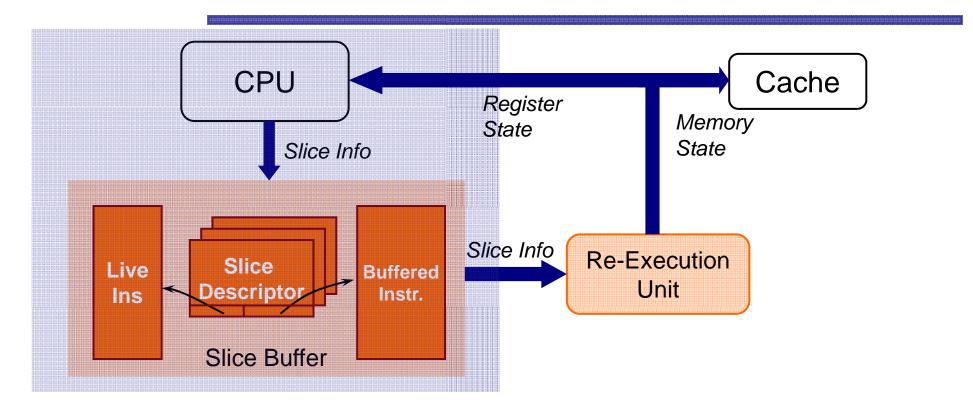

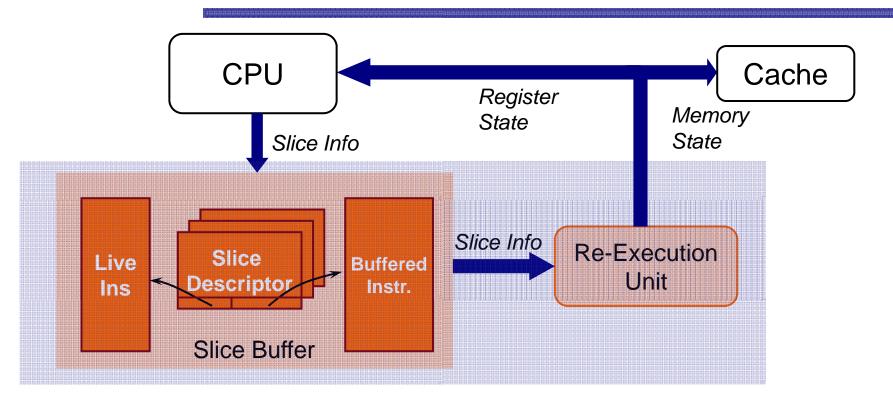

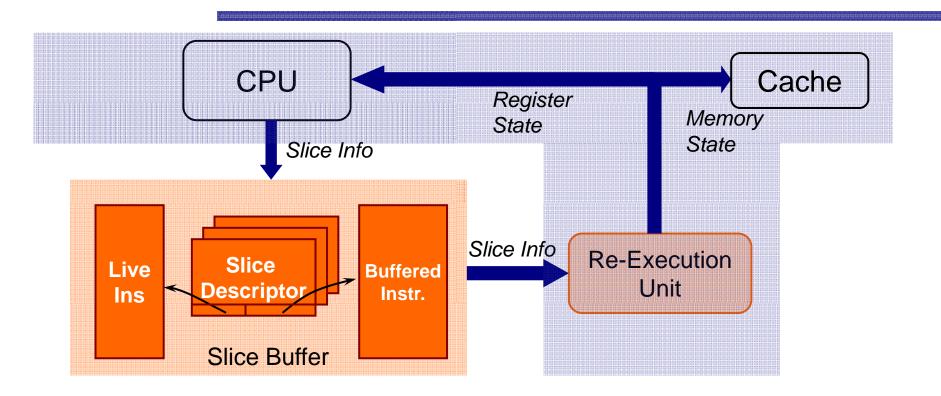

### Architecture Design

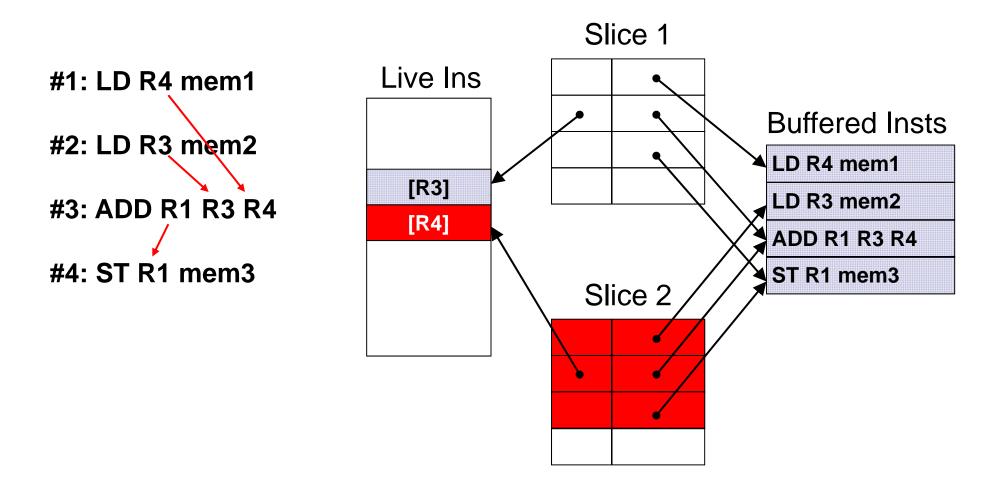

## **Step 1: Slice Collection**

- Fill up the Slice Buffer when a prediction is made

- Track both register and memory dependence

- Save live-in operands and slice instructions

- Slices are buffered when instructions are retired

#### An Example

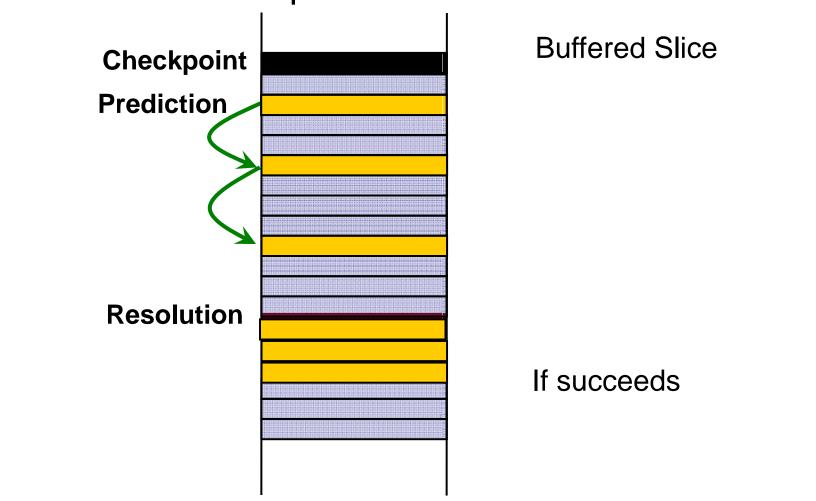

## Step 2: Slice Re-Execution

- REU takes over after a violation is verified

- In-order execution

- Sufficient condition is checked during the re-execution

- If succeeds, merge the register and memory state; otherwise, squash the task and restart

# Step 3: State Merging

- Copy live registers back to the main process register file

- Merge memory state (details please see the paper)

## **Multiple Overlapping Slices**

One slice might corrupt live-ins of the other slice

#### Outline

- Motivation and Contributions

- Idea of ReSlice

- Architecture Design

- Experimental Results

- Conclusions

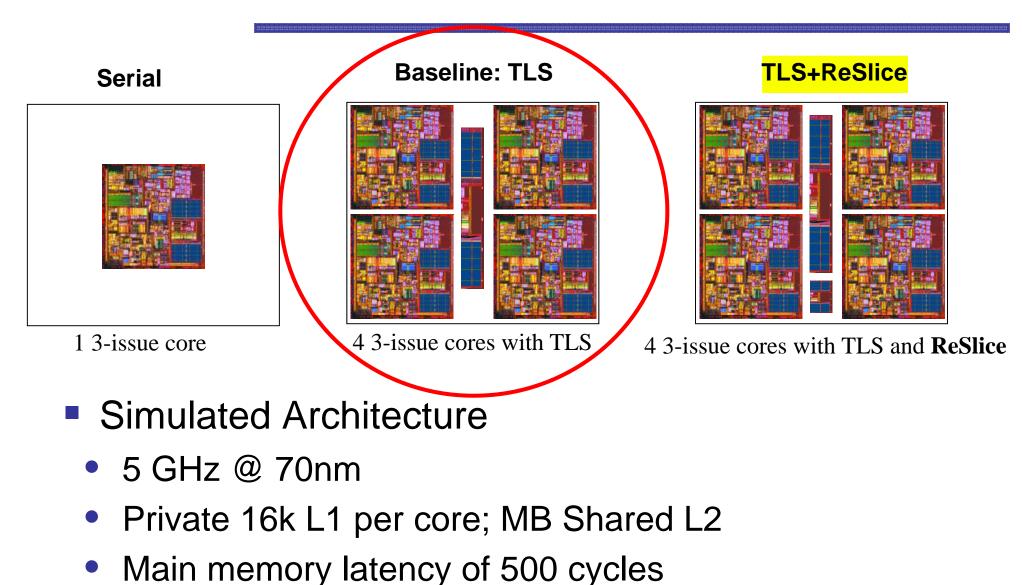

# Methodology

About 0.75-1.50 Billion instructions simulated

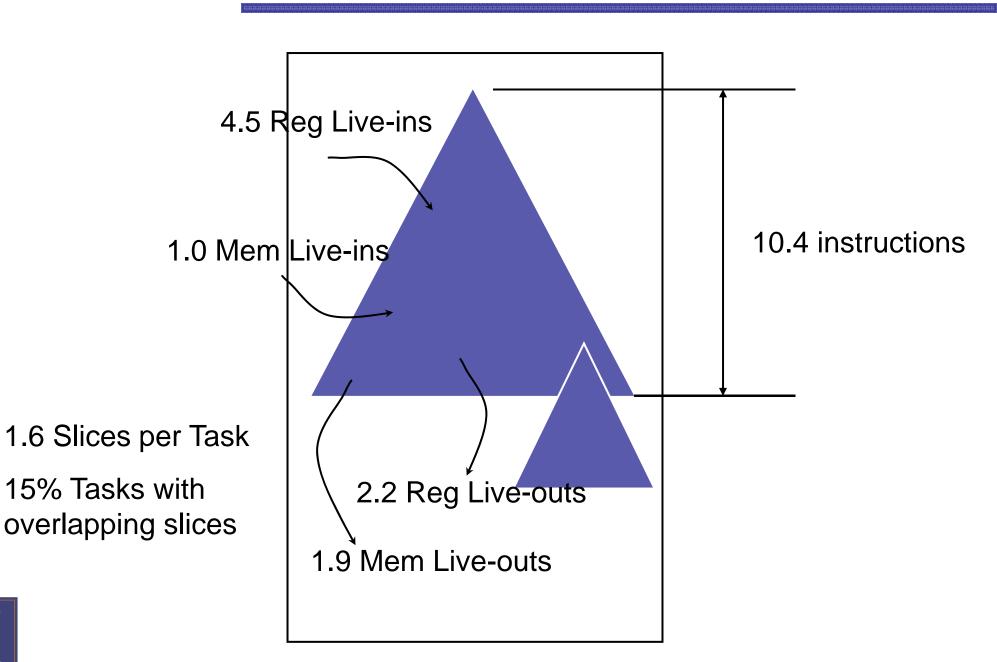

#### **Slice Characterization**

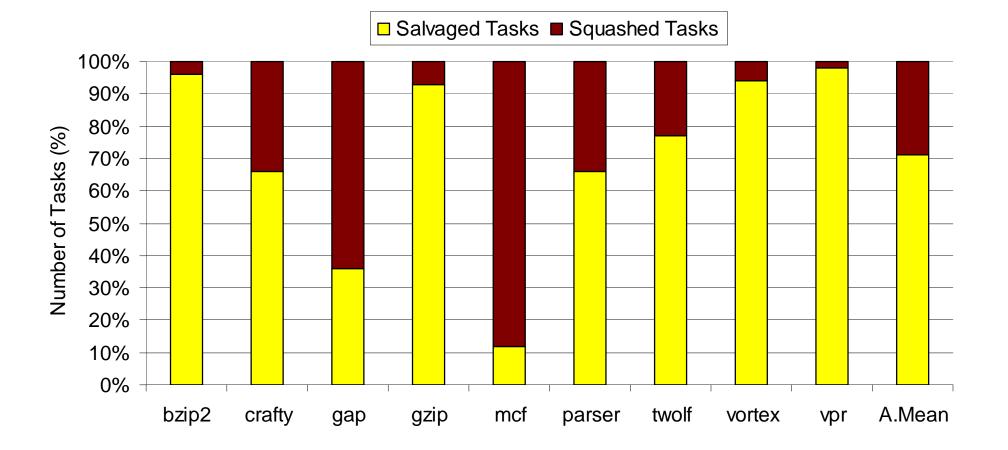

#### Accuracy of ReSlice

More 70% tasks are salvaged because of ReSlice

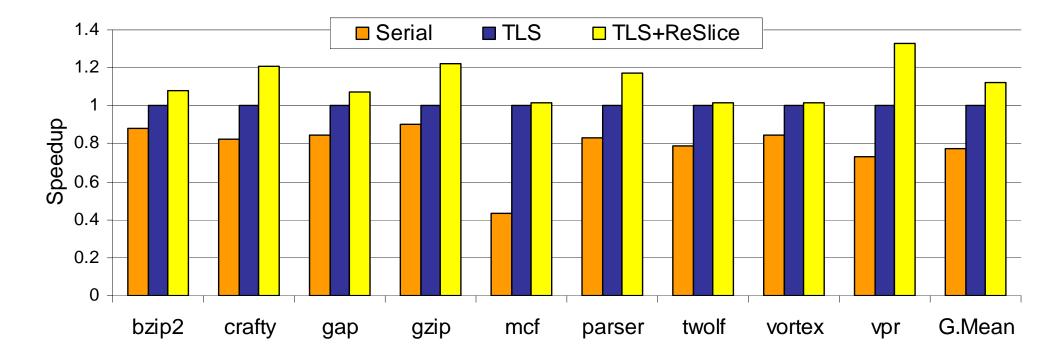

#### Performance

TLS+ReSlice speeds up 12% over TLS and 45% over Serial

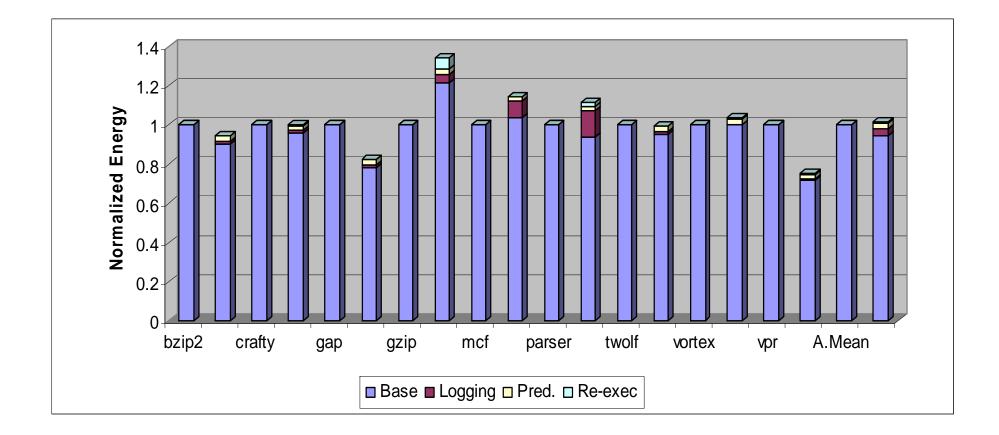

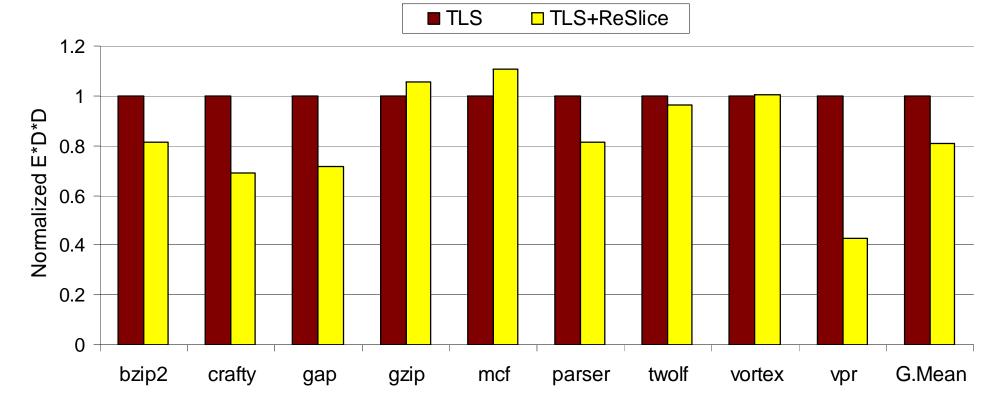

# Energy × Delay<sup>2</sup>

E×D<sup>2</sup> reduction: 20% over TLS

#### Conclusions

- Generic Architecture for Forward slice re-execution

- A Sufficient Condition for correct re-execution and merge

- Improve state of the art TLS on SpecInt

- Speedups: 1.12 over TLS, 1.45 over Serial

- E×D<sup>2</sup> reduction: **20%** over TLS

- Recovering wasted work is a promising approach

- Boost performance

- Energy efficient

# Selective Re-execution of Long-retired Misspeculated Instructions Using Forward Slicing

Smruti R. Sarangi, Wei Liu, Josep Torrellas, Yuanyuan Zhou

University of Illinois at Urbana-Champaign

http://iacoma.cs.uiuc.edu