### Runnemede: an Architecture for Ubiquitous High-Performance Computing

Nicholas Carter, Aditya Agrawal, Shekhar Borkar, Romain Cledat, Howard David, Dave Dunning, Joshua Fryman, Ivan Ganev, Roger A. Golliver, Rob Knauerhase, Richard Lethin, Benoit Meister, Asit K. Mishra, Wilfred R. Pinfold, Justin Teller, Josep Torrellas, Nicolas Vasilache, Ganesh Venkatesh, Jianping Xu

- INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL® PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

- Intel may make changes to specifications and product descriptions at any time, without notice.

- All products, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice.

- Intel, processors, chipsets, and desktop boards may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Code names featured are used internally within Intel to identify products that are in development and not yet publicly.

- Code names featured are used internally within Intel to identify products that are in development and not yet publicly

announced for release. Customers, licensees and other third parties are not authorized by Intel to use code names in

advertising, promotion or marketing of any product or services and any such use of Intel's internal code names is at the

sole risk of the user

- Performance tests and ratings are measured using specific computer systems and/or components and reflect the

approximate performance of Intel products as measured by those tests. Any difference in system hardware or software

design or configuration may affect actual performance.

- Intel, Intel Inside, and the Intel logo are trademarks of Intel Corporation in the United States and other countries.

- \*Other names and brands may be claimed as the property of others.

- Copyright © 2009 Intel Corporation.

- This research was, in part, funded by the U.S. Government. The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the U.S. Government.

### **DARPA UHPC Program**

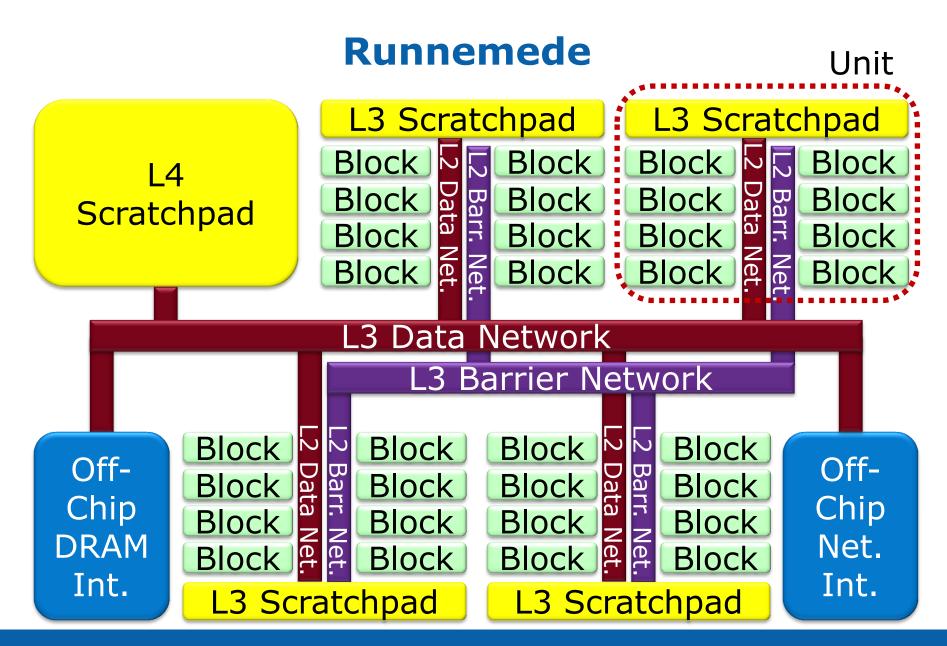

# Runnemede: Intel's UHPC research architecture

### 50 GOPS/Watt

### Ubiquitous

Intel Labs

**3** February 25, 2013

Public

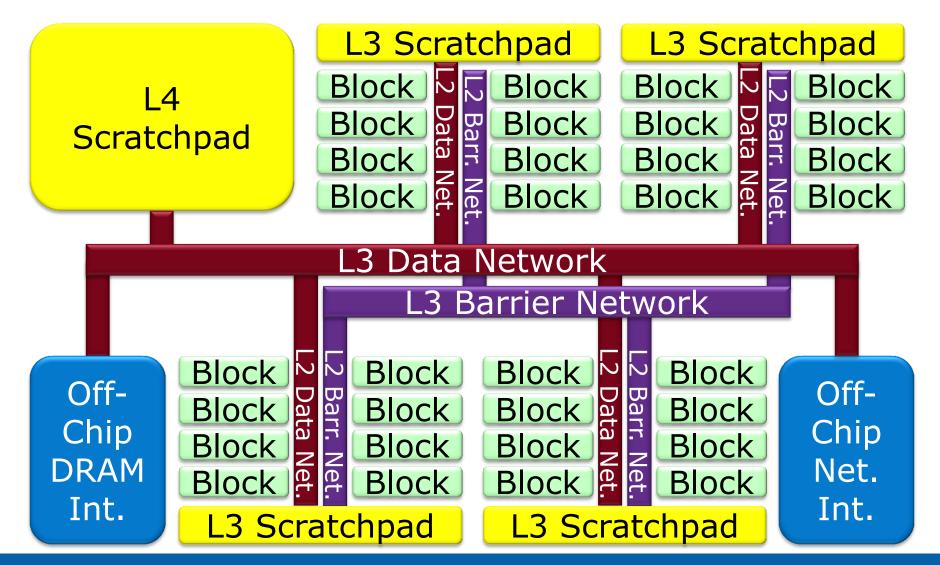

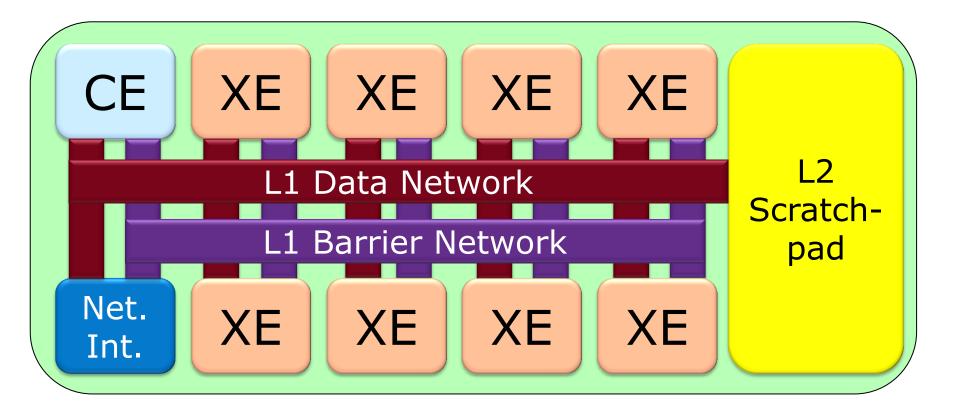

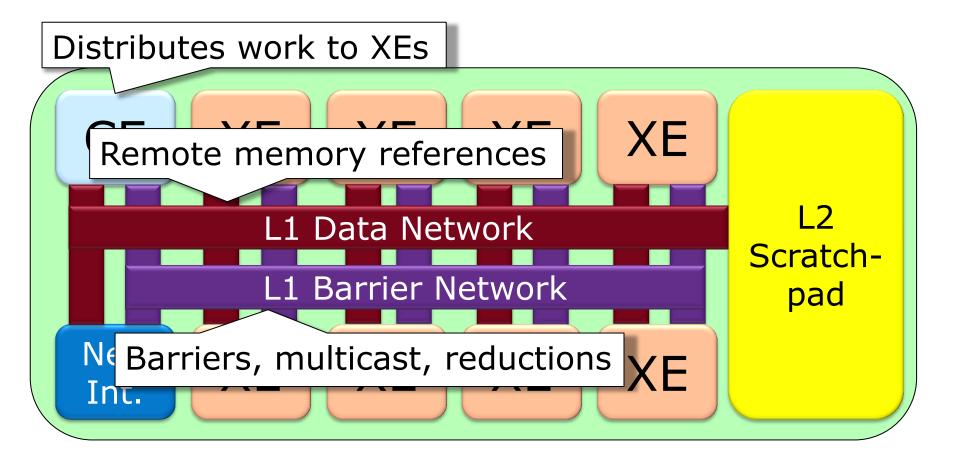

### **A Runnemede Chip**

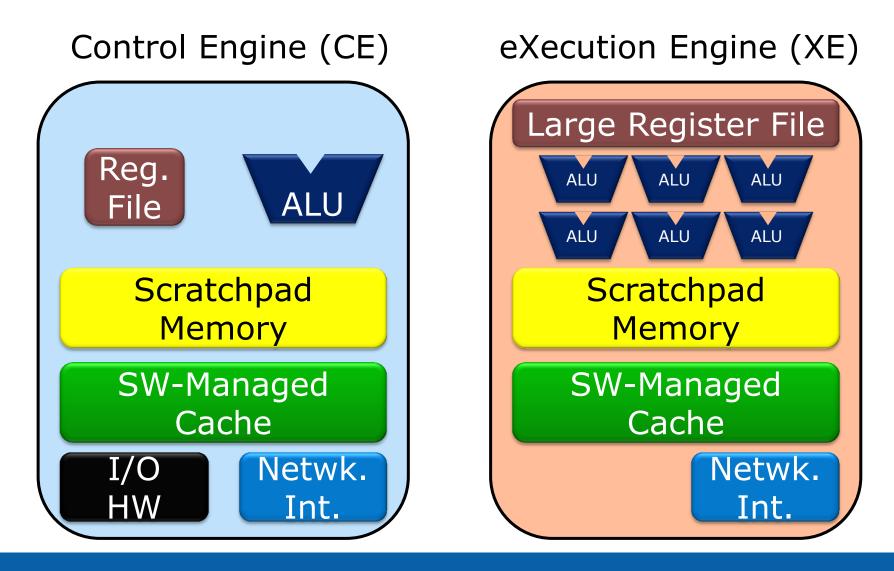

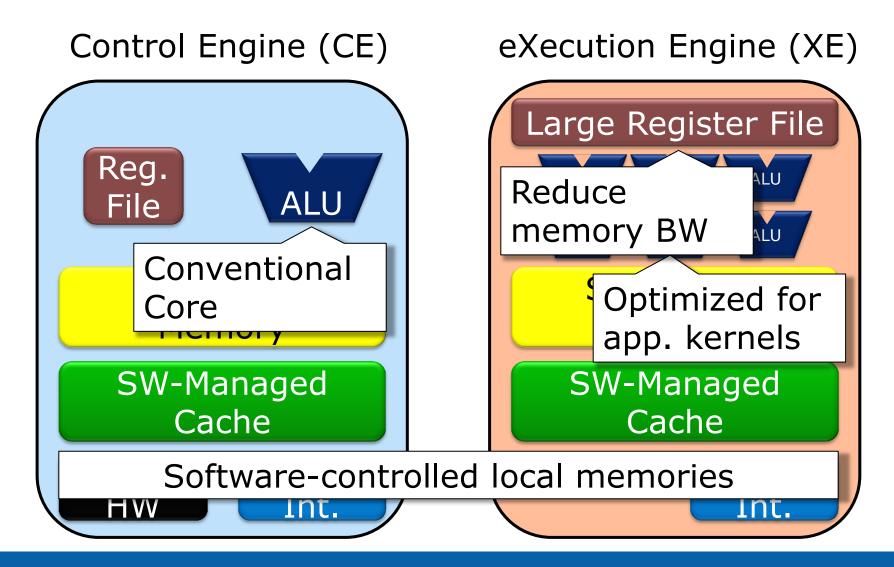

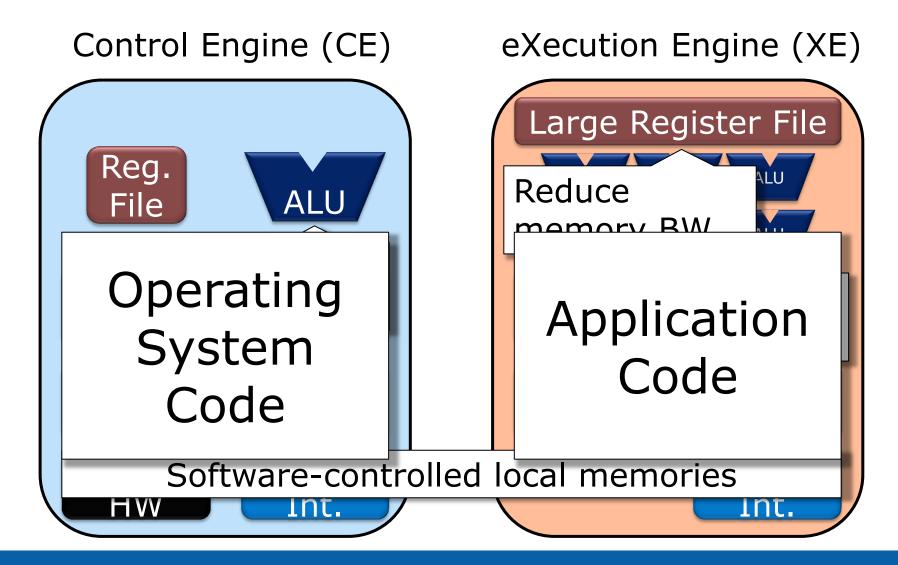

#### **Heterogeneous Cores**

#### **Heterogeneous Cores**

#### **Heterogeneous Cores**

### **Blocks: Cores Grouped for Locality**

### **Blocks: Cores Grouped for Locality**

### **Case Studies**

- Co-design for Synthetic Aperture Radar

- Scratchpads vs. caches

- Network analysis (in paper)

# <u>Energy unit</u>: double-precision floating-point multiply (FM64)

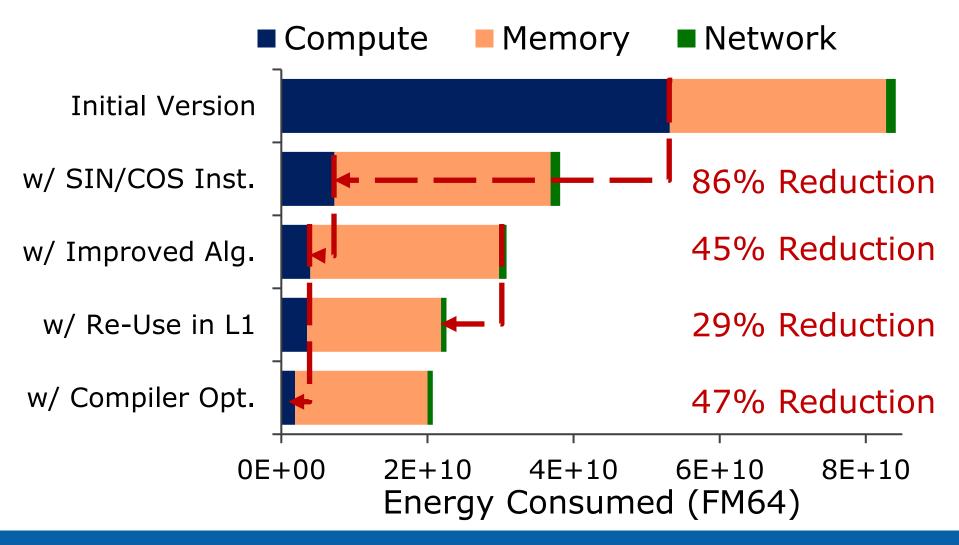

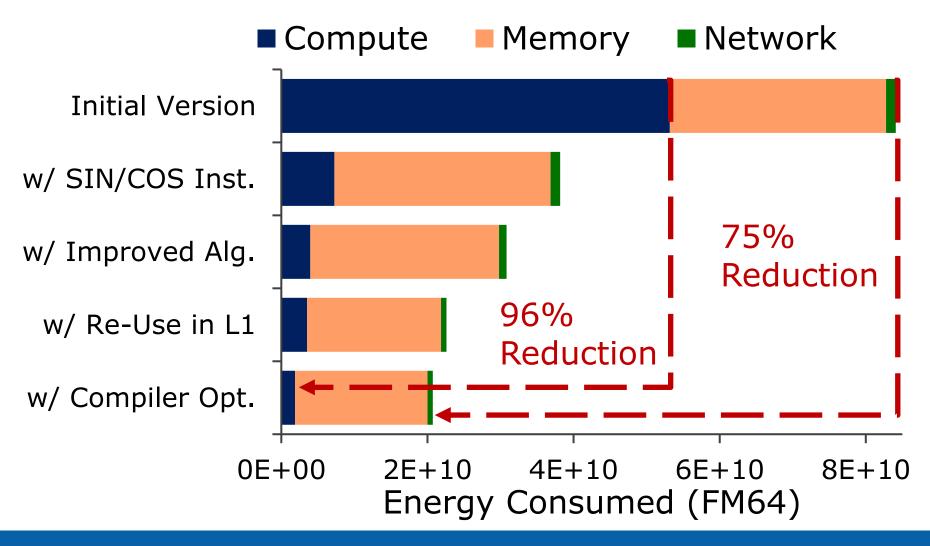

## **Co-Design for Synthetic Aperture Radar** SAR: UHPC "challenge problem"

# HW, SW co-designed for energy efficiency

### **Codesign for Synthetic Aperture Radar**

### **Codesign for Synthetic Aperture Radar**

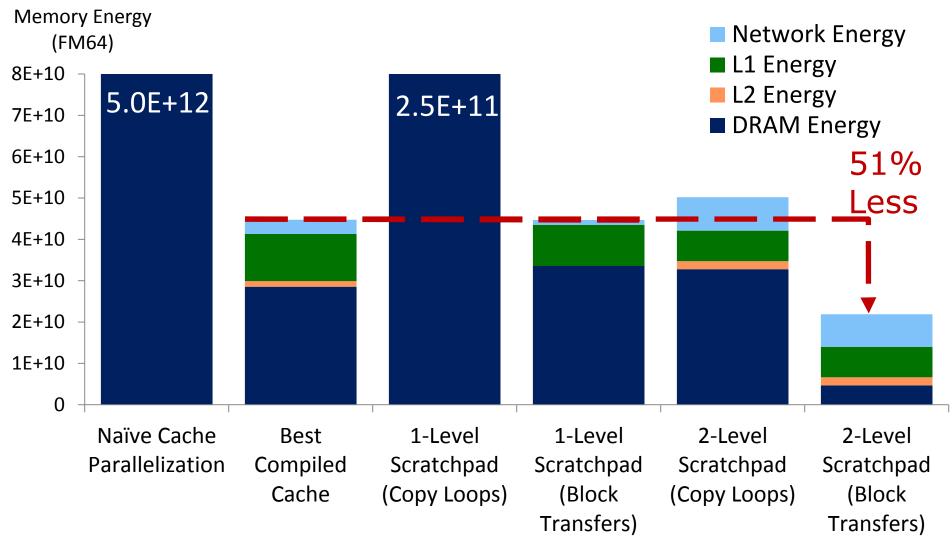

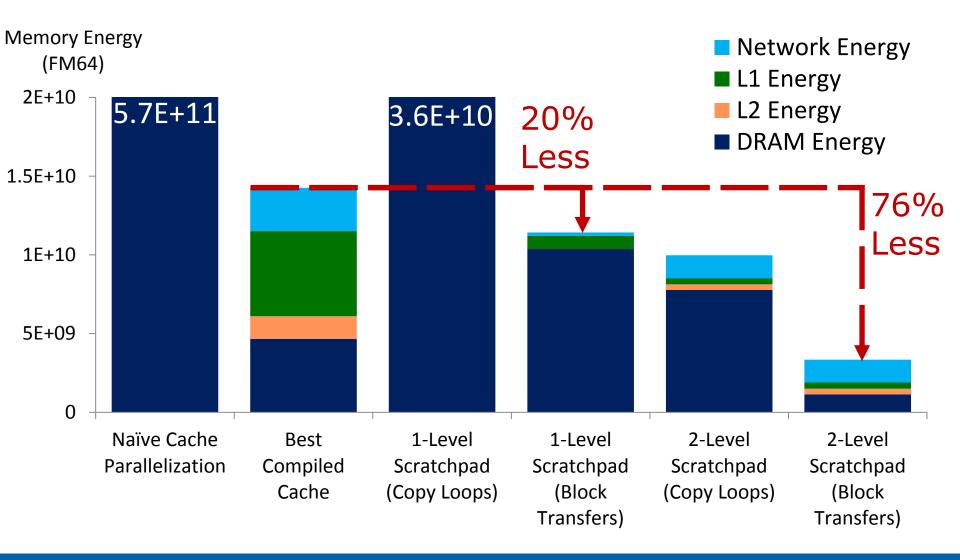

### **Comparing Scratchpads and Caches**

### Questions:

- Energy?

- Programming Effort?

### **Matrix Multiplication**

### **Givens QR Decomposition**

### Conclusion

Runnemede is an energy-optimized research architecture

- •NTV circuits, power/clock gating, co-design, SW-managed memory

- Co-design: 4x energy improvement

- •SW-managed memory: 2-4x memory energy improvement